Представлены результаты тестирования [1] энергонезависимой CXL DRAM в составе совместного решения Lenovo (experimental Lenovo x86 Server), Samsung (Samsung CXL Memory Expander) и VMware (experimental version vSphere ESXi) при организации архитектуры двухсокетных серверов с многоуровневой памятью. Серверы Lenovo с поддержкой CXL должны быть доступны для заказа уже в ближайшей перспективе.

Грегори Пруэтт (Gregory Pruett),

главный инженер Lenovo Infrastructure Solutions Group.

Введение

В ближайшие 3 года технологии памяти изменятся — новые типы памяти и стандарты преобразуют конфигурацию серверов и способы использования памяти приложениями. Сегодня серверы разработаны со слотами DIMM, напрямую подключенными к каждому процессору. В поколениях Intel «Ice Lake» и AMD «Rome/Milan» каждый ЦП имеет 8 каналов памяти с 2 модулями DIMM на канал. Таким образом, двухпроцессорный сервер имеет максимум 32 модуля DIMM. Скорость памяти, тип памяти (например, DDR4) и максимальная емкость регулируются архитектурой ЦП. Это скоро изменится. В дополнение к традиционным модулям памяти DIMM появятся другие типы модулей памяти, и их можно будет установить в слоты PCIe, отсеки для дисков NVMe или в отсеки с общей памятью.

Эта новая возможность основана на отраслевом стандарте Compute Express Link (CXL). С появлением нового стандарта CXL будущие серверы смогут подключать устройства когерентной памяти к системной памяти. Эти устройства CXL.mem могут использовать или добавлять память в систему. Например, память можно установить на адаптер CXL, который подходит к стандартному слоту PCIe.

CXL может даже подключать память с разными характеристиками производительности (рис. 1). Более медленная память с более высокой задержкой или меньшей пропускной способностью может быть подключена к слоту CXL без отрицательного воздействия на производительность каналов DIMM или других разъемов CXL. Диски, подключенные к PCIe, также могут поддерживать память CXL, как энергозависимую память DRAM, так и постоянную память.

Рис. 1. Новые форм-факторы памяти/флеш-устройств для архитектуры серверов с многоуровневой памятью.

Почему все это имеет значение? Во-первых, больше слотов и новые модули памяти большего размера могут предоставить варианты для более дешевых конфигураций памяти. Во-вторых, серверы следующего поколения позволят использовать разные «уровни» памяти. Например, один сервер может содержать как высокопроизводительную (небольшую, дорогую) память, так и память большой емкости (более медленную, дешевую). Высокопроизводительная память может улучшить рабочие нагрузки, такие как высокопроизводительная обработка транзакций OLTP, для обработки миллионов онлайн платежей в секунду. Память большой емкости может хорошо подходить для аналитических задач, которым необходимо выделять большие объемы памяти, но которые гораздо менее чувствительны к пропускной способности или задержке. Теперь обе рабочие нагрузки можно объединить для работы на одном сервере с разными уровнями обслуживания памяти.

Расширение памяти с помощью энергозависимой DRAM с подключением по CXL

Предполагается, что уже к 2023 году CXL станет практической технологией для расширения энергозависимой когерентной памяти. Lenovo также ожидает, что процессоры от различных производителей будут иметь интегрированные хост-мосты и контроллеры CXL. И, наконец, ожидается появление конечных устройств с локальным контроллером памяти DDR.

В этой области уже есть разработки: например, недавняя презентация расширителя памяти Samsung CXL (Samsung CXL Memory Expander). Это «первый в отрасли модуль памяти, поддерживающий новый стандарт межсоединений Compute Express Link (CXL) и интегрированный с технологией Samsung Double Data Rate 5 (DDR5) [2].

При доступе к напрямую подключенной энергозависимой памяти CXL возникает задержка, которая примерно эквивалентна “задержке памяти на 1 переход” (“1hop memory latency”). Рассмотрим сервер (рис. 2) с двумя сокетами ЦП (CPU0 и CPU1). Ядро от CPU0, обращающееся к DRAM, напрямую подключенное к контроллеру памяти на CPU0, будет иметь заданную задержку «N». (Эта задержка на реальных процессорах может составлять от ~ 80 до 100 нс).

Рис. 2. Задержка перехода между процессорами (1-hop memory latency) может составлять примерно от 50 до 70 нс.

Также существует задержка «H» для ядра на CPU0 для отправки и получения запроса к/от CPU1 по межпроцессорному соединению (для x86 это будет UPI или XGMI в зависимости от производителя процессора). Эта последняя задержка известна как задержка перехода между процессорами, которая может составлять примерно от 50 до 70 нс.

В настоящее время в многопроцессорных серверах x86 используются однородные процессоры, поэтому средняя задержка памяти должна быть одинаковой независимо от процессора. Таким образом, «задержка памяти на одном переходе» равна «N + 1 * H», то есть задержка при однократном переходе, как показано на рис. 2. Ожидается, что CXL-доступ к памяти на локальном ЦП (для ядра на CPU0 для CXLдоступа к памяти DRAM CPU0 с прямым подключением) будет примерно таким же, как задержка при однократном переходе (single-hop latency). Для ядра на CPU1 при доступе к CXL DRAM, подключенной к CPU0, ожидается задержка «N + 2 * H» или двухэтапная задержка. Поскольку существующие гипервизоры, операционные системы и приложения уже хорошо протестированы на задержку в 1 и 2 перехода (1-hop latency и 2-hop latency), теоретически память, подключенная к CXL, должна быть в высокой степени совместима и хорошо работать с существующей программной экосистемой.

Уровни памяти в будущем и CXL

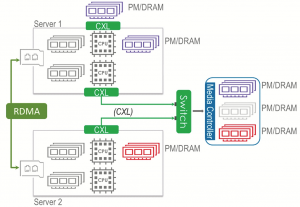

Когерентное соединение CXL делает возможным как внутрисерверное (локальное) расширение памяти, так и межсерверное объединение и совместное использование памяти (рис. 3). Сложные программные оркестраторы, гипервизоры и операционные системы будут уравновешивать потребности в задержке, полосе пропускания, сохраняемости и гранулярности доступа (байты против блоков) уровней памяти при размещении рабочих нагрузок и виртуальных машин на правильном сервере с соответствующим выбором и распределением памяти. По умолчанию управление уровнями памяти и их распределение должны быть прозрачными для реальных рабочих нагрузок и виртуальных машин, если необходимо поддерживать гибкость оборудования, не нарушая при этом критически важные стеки клиентских решений.

Рис. 3. Когерентное соединение CXL делает возможным как внутрисерверное (локальное) расширение памяти, так и межсерверное объединение и совместное использование памяти.

Благодаря успешному многоуровневому распределению памяти в CXL заказчики могут лучше использовать свои вложения в память и хранилище и обеспечить большую гибкость и детализацию при обновлении этих вложений.

Энергозависимая CXL-память больше не является теорией

Для тестирования энергонезависимой CXL-памяти компанией Lenovo была запущена экспериментальная версия VMware vSphere ESXi на специально разработанном сервере в следующей конфигурации (рис. 4):

- двухпроцессорный экспериментальный сервер Lenovo с процессором x86;

- CPU0: 128 GiBDDR5 DRAM и 128 GiB от расширителя памяти SamsungCXL;

- CPU1: только 16 GiB DRAM;

- в BIOS CXL Samsung DRAM размещалась в Memory-Only NUMA (Non-Uniform Memory Access «неравномерный доступ к памяти» или Non-Uniform Memory Architecture «архитектура с неравномерной памятью», https://ru.wikipedia.org/wiki/Non-Uniform_Memory_Access) таблице соответствия только для CPU0.

Рис. 4. Двухсокетная конфигурация сервера для тестирования энергонезависимости CXL-памяти.

Первая реальная демонстрация поддержки x86 гипервизора с использованием CXL DRAM для виртуальных машин

Высокая стабильность конфигурации в лаборатории Lenovo позволила успешно включать, запускать и выключать 4 виртуальных машины (ВМ), работающих на экспериментальной версии VMware vSphere (в которой не было изменений, специально пред назначенных для поддержки CXL).

Каждая ВМ была сконфигурирована с 2-vCPU и 64 GiB DRAM и выполняла простой тест, который потреблял 60 GiB DRAM. ВМ не знали об уровне памяти CXL (и не должны были знать). ВМ запускались поэтапно, чтобы было понятно, как используется память сервера. Отредактированный (сжатая шкала времени и вырезанные из видео циклы простоя) снимок экрана из видео окна мониторинга памяти VMware vSphere Web UI, работающего в этой системе, показан на рис. 5.

Рис. 5. Снимок экрана из видео окна мониторинга памяти VMware vSphere Web UI.

Для использования DRAM общего назначения Lenovo UEFI BIOS создал 3 узла памяти (неоднородный доступ к памяти – NUMA) (диапазон адресов DRAM) и привязал их к CPU0 и CPU1, как показано на рис. 6. Экспериментальная версия vSphere правильно перечислила эти 3 узла и назначила DRAM соответствующим виртуальным машинам – хорошая демонстрация прозрачного многоуровневого распределения памяти CXL в действии:

- узел для 128 GiB DRAM на CPU0;

- узел для 128 GiB CXL DRAM, напрямую подключенный к CPU0;

- узел для 16 GiB DRAM на CPU

Рис. 6. Аннотированный снимок экрана «esxtop», когда ВМ работали на сервере Lenovo.

ВМ Photon 11 и Photon 12 были привязаны в файле .vmx к CPU0 и в основном используют доступную память DRAM из этого процессора. ВМ Photon 21 и Photon 22 были привязаны в файле .vmx к CPU1 и использовали всю доступную DRAM из памяти CPU1 и значительную часть CXL DRAM, доступную на другом сокете. Это показывает, что VMware vSphere смогла правильно и прозрачно управлять характеристиками задержки при использовании удаленной DRAM CXL для удовлетворения потребностей ВМ Photon 21 и Photon 22.

Рис. 6 представляет собой аннотированный снимок экрана «esxtop», когда эти виртуальные машины работали на сервере Lenovo. В строке «NUMA / MB:» можно увидеть, что каждый из 3 узлов памяти NUMA активно используется.

Каждая запись отображается как «MAX_MEMORY_IN_MB (REMAINING_FREE_MEMORY_IN_MB)».

Заключение

Проведенное тестирование является хорошим примером того, как CXL DRAM понимается серверами и гипервизорами, поддерживающими многоуровневую память, прозрачным для виртуальных машин образом. За этим стоит огромный объем работы и сотрудничество множества компаний:

- производитель ЦП x86 не только реализовал контроллер CXL хост-моста в прототипе ЦП и проверил его с помощью расширителя памяти Samsung CXL, но также позволил запустить демонстрацию VMworld на этом ЦП;

- Lenovo разработала, внедрила и предоставила прототип сервера с этим процессором в лаборатории Lenovo;

- компания Samsung разработала расширитель памяти Samsung CXL, предоставила несколько образцов, а также поддержала Lenovo в процессе тестирования;

- разработанная VMware vSphere позволила запустить экспериментальную версию vSphere на экспериментальном сервере Lenovo без каких-либо проблем.

Будущие процессоры планируют поддерживать CXL Memory и Accelerator expansion, а новые форм-факторы памяти обеспечат гибкость при их применении. Программное обеспечение сможет легко использовать технологию CXL, поскольку она строится на хорошо понятных интерфейсах, которые уже присутствую в составе серверов с несколькими процессорами. И, начиная с 2023 года, стоит задуматься об использовании серверов с расширениями на базе CXL.

Грегори Пруэтт (Gregory Pruett), Lenovo Infrastructure Solutions Group

Источники, доп. ресурсы

[1] CXL and the Tiered-Memory Future of Servers, Oct. 06, 2021. Coauthored by Richard A. Brunner, Principal Engineer, CTO Server Platform Technologies, VMware Inc – https://www.lenovoxperience.com/newsDetail/283yi044hzgcdv7snkrmmx9ovpq6aesmy9u9k7ai2648j7or.

[2] VMworld 2021 session VI2334 – Rich Brunner, Greg Pruett – “Prepared for the New Memory Technology in Next Year’s Enterprise Servers?” – https://myevents.vmware.com/widget/vmware/vmworld2021/catalog?tab.contentcatalogtabs=1627421929827001vRXW&search=2334.

[3] VMworld 2021 session VI2342 – Marcos Aguilera – “The Big Memory Transformation [VI2342] ” – https://myevents.vmware.com/widget/vmware/vmworld2021/catalog?tab.contentcatalogtabs=1627421929827001vRXW&search=2342.

[4] VMworld 2021 session MCL2384 – Suds Jain, Ryan Baxter, Muge Tanik, David Wang, “Big Memory – An Industry Perspective on Customer Pain Points and Potential Solutions” – https://myevents.vmware.com/widget/vmware/vmworld2021/catalog?tab.contentcatalogtabs=1627421929827001vRXW&search=2384.

[5] Samsung CXL Memory Expander – https://news.samsung.com/global/samsung-unveils-industry-first-memory-module-incorporating-new-cxl-interconnect-standard.

[6] Compute Express Link (CXL) Consortium – https://www.computeexpresslink.org.

[7] SNIA Drive Form Factors (EDSFF, U.2, M.2) – https://www.snia.org/forums/cmsi/knowledge/formfactors.

[8] Lenovo ThinkAgile VX portfolio – https://www.lenovo.com/us/en/datacenter/software-defined-infrastructure/ThinkAgile-VX-Series.

[9] Lenovo XClarity Integrator for VMware vCenter / vSphere Lifecycle Manager – https://support.lenovo.com/us/en/solutions/lnvo-vmware.

[10] Lenovo TruScale Infrastructure Services – https://www.lenovo.com/us/en/data-center/services/truscale-infrastructure-services.

Авторы: Гантимуров А.П., Калашник А.Г.

Отслеживать

Отслеживать